|

市場調查報告書

商品編碼

1567379

FE·先進封裝金屬化學品市場:2024年~2025年(Critical Materials Report)Metal Chemicals for FE & Advanced Packaging Market Report 2024-2025 (Critical Materials Report) |

||||||

價格

本報告調查了FE/先進封裝的金屬化學品市場,並提供了應用於先進封裝(晶圓級)和半導體裝置製造(鑲嵌製程)的金屬化學品市場的趨勢和供應鏈信息,內容非常全面。銅電鍍和添加劑趨勢、市場佔有率、技術趨勢和供應商概況。附錄中還包括供應商產品比較圖,總結了先進封裝中使用的電鍍產品的公開資訊。

資訊圖表

目錄

第1章 摘要整理

第2章 調查範圍,目的,手法

第3章 半導體產業的市場預測

- 全球經濟與整個產業的展望

- 以電子產品細分市場劃分的晶片銷售額

- 半導體製造業的成長與擴張

- 政策和貿易趨勢及影響

- 半導體材料概述

第4章 各市場區隔金屬化學品市場

- 定義

- 金屬電鍍化學品市場概覽

- 先進封裝金屬化 - 市場推動因素

- 晶片互連成長趨勢

- 電鍍化學品金屬礦的位置

- IC電鍍中使用的金屬的潛在瓶頸

- 未來可能面臨的需求價格壓力

第5章 技術趨勢

- 半導體金屬鍍金所使用的化學物質

- 封裝技術趨勢

- 技術趨勢

第6章 競爭情形

- 先進封裝與互連市場佔有率總計

- OEM市佔率-電鍍設備

- 按應用劃分的市場佔有率 - 用於先進封裝的 CU 電鍍

- 區域進入者和其他人

- 併購活動

第7章 分析師的評估

- 先進的金屬鍍金的應用市場評估

第8章 供應商簡介

- BASF

- DUPONT

- CHANG CHUN GROUP

- INCHEON CHEMICAL COMPANY

- ISHIHARA CHEMICAL/UNICON

- 其他9公司

第9章 附錄A:封裝技術趨勢

- 科技的課題

- 金屬清潔面臨的挑戰

- 市場趨勢

- 晶圓級電鍍 - 第一級互連

- 先進封裝應用的市場推動因素

- 晶圓級封裝架構

- 技術趨勢-RDL

- 小晶片架構的市場推動因素

- TSV 填充 2.5-3D

- 包裝電鍍要求

This report covers the Metal Chemicals market trends and supply-chain as it applied to Advanced Packaging (wafer level) and Semiconductor Device Manufacturing (damascene process). Included are forecasts for copper plating and additives, market shares, technical trends, and supplier profiles. Also included in the appendix is a supplier product comparison table of publicly available information on plating products used for advanced packaging.

INFOGRAPHICS

TABLE OF CONTENTS

1 EXECUTIVE SUMMARY

- 1.1 EXECUTIVE SUMMARY

- 1.2 ADVANCED PACKAGING PER WAFER STARTS

- 1.3 DEVICE DEMAND DRIVERS - LOGIC

- 1.4 CU PLATING FORECAST FOR CU INTERCONNECTS AND ADVANCED PACKAGING

- 1.5 MARKET SHARES

- 1.6 SUPPLIER ACTIVITIES - VARIOUS ANNOUNCEMENTS

- 1.7 RISK FACTORS

- 1.8 ANALYST ASSESSMENT

2 SCOPE, PURPOSE AND METHODOLOGY

- 2.1 SCOPE

- 2.2 PURPOSE & METHODOLOGY

- 2.3 OVERVIEW OF OTHER TECHCET CMR REPORTS

3 SEMICONDUCTOR INDUSTRY MARKET OUTLOOK

- 3.1 WORLDWIDE ECONOMY AND OVERALL INDUSTRY OUTLOOK

- 3.1.1 SEMICONDUCTOR INDUSTRIES TIES TO THE GLOBAL ECONOMY

- 3.1.2 SEMICONDUCTOR SALES GROWTH

- 3.1.3 TAIWAN OUTSOURCE MANUFACTURER MONTHLY SALES TRENDS

- 3.2 CHIPS SALES BY ELECTRONIC GOODS SEGMENT

- 3.2.1 ELECTRONICS OUTLOOK

- 3.2.2 AUTOMOTIVE INDUSTRY OUTLOOK

- 3.2.3 SMARTPHONE OUTLOOK

- 3.2.4 PC OUTLOOK

- 3.2.5 SERVERS / IT MARKET

- 3.3 SEMICONDUCTOR FABRICATION GROWTH & EXPANSION

- 3.3.1 IN THE MIDST OF HUGE INVESTMENT IN CHIP EXPANSIONS

- 3.3.2 NEW FABS IN THE US

- 3.3.3 WW FAB EXPANSION DRIVING GROWTH

- 3.3.4 EQUIPMENT SPENDING TRENDS

- 3.3.5 ADVANCED LOGIC TECHNOLOGY ROADMAPS

- 3.3.6 FAB INVESTMENT ASSESSMENT

- 3.4 POLICY & TRADE TRENDS AND IMPACT

- 3.5 SEMICONDUCTOR MATERIALS OVERVIEW

- 3.5.1 TECHCET WAFER STARTS FORECAST THROUGH 2028

- 3.5.2 TECHCET MATERIALS MARKET FORECAST THROUGH 2028

4 METAL CHEMICALS MARKET BY SEGMENT

- 4.1 DEFINITIONS

- 4.2 METAL PLATING CHEMICALS MARKET OVERVIEW

- 4.2.1 OVERVIEW - CU ADVANCED PACKAGING AND CHIP INTERCONNECTS METALLIZATION

- 4.2.2 OVERVIEW - PLATING MARKET TRANSITIONAL TRENDS

- 4.3 ADVANCED PACKAGING METALLIZATION - MARKET DRIVERS

- 4.3.1 ADVANCED PACKAGING - ADDITIVES FOR CU PLATING REVENUE

- 4.3.2 ADVANCED PACKAGING - COPPER CHEMICALS REVENUE

- 4.3.3 ADVANCED PACKAGING ADDITIVE VOLUMES

- 4.3.4 OTHER PLATING MATERIALS FOR ADVANCED PACKAGING

- 4.3.5 SN / SNAG PLATING

- 4.4 CHIP INTERCONNECTS GROWTH TRENDS

- 4.4.1 CHIP INTERCONNECTS GROWTH DRIVERS

- 4.4.2 CHIP INTERCONNECTS CU PLATING REVENUES

- 4.4.3 CHIP INTERCONNECTS ADDITIVE VOLUMES

- 4.5 MINE LOCATIONS FOR METALS IN PLATING CHEMICALS

- 4.6 POSSIBLE CHOKE POINTS FOR METALS USED IN IC PLATING

- 4.7 FUTURE POSSIBLE DEMAND PRICE PRESSURES

5 TECHNICAL TRENDS

- 5.1 CHEMISTRIES USE FOR SEMICONDUCTOR METAL PLATING

- 5.2 PACKAGING TECH TRENDS

- 5.2.1 PACKAGING TECHNICAL CHALLENGES

- 5.3 TECH TRENDS

- 5.3.1 MARKET DRIVES TECHNOLOGY TRENDS

- 5.3.2 ADV LOGIC INTERCONNECT WIRING TECHNOLOGY EVOLUTION

- 5.3.3 CU INTERCONNECTS QUALIFICATION REQUIREMENTS

- 5.3.4 LOGIC METALLIZATION ROADMAP

- 5.3.5 ADV LOGIC BURIED POWER RAIL

- 5.3.6 TECHNOLOGY ROADMAP: DRAM WITH MO OR RU

- 5.3.7 PRECURSOR TECHNOLOGY ROADMAP: 3D NAND USING MO OR RU

- 5.3.8 EXAMPLE OF LOGIC PRO CESS FLOW 20 NM TO 32 NM LOGIC PVD

- 5.3.9 TECHNICAL REQUIREMENTS SUMMARY 1/2

6 COMPETITIVE LANDSCAPE

- 6.1 TOTAL ADVANCED PACKAGING AND INTERCONNECTS MARKET SHARES

- 6.2 OEM MARKET SHARE - PLATING EQUIPMENT

- 6.3 MARKET SHARE BY APPLICATION - CU PLATING FOR ADVANCED PACKAGING

- 6.4 REGIONAL PLAYERS AND OTHERS

- 6.5 M&A ACTIVITY

7 ANALYST ASSESSMENT

- 7.1 ADVANCED METAL PLATING APPLICATIONS MARKET ASSESSMENT

8 SUPPLIER PROFILES

- BASF

- DUPONT

- CHANG CHUN GROUP

- INCHEON CHEMICAL COMPANY

- ISHIHARA CHEMICAL/UNICON

- ...AND 9 MORE

9 APPENDIX A: PACKAGING TECH TRENDS

- 9.1 TECHNOLOGY CHALLENGE

- 9.1.1 METAL CLEANINGS CHALLENGE

- 9.1.2 MARKET DYNAMIC

- 9.1.3 WAFER LEVEL PLATING-FIRST LEVEL INTERCONNECT

- 9.1.4 MARKET DRIVERS OF ADVANCED PACKAGING APPLICATIONS

- 9.1.5 WAFER LEVEL PACKAGING ARCHITECTURES

- 9.1.6 TECH TRENDS- RDL

- 9.1.7 MARKET DRIVERS OF CHIPLET ARCHITECTURE

- 9.1.8 TSV FILLING 2.5-3D

- 9.1.9 PACKAGING ELECTROPLATING REQUIREMENTS

LIST OF FIGURES

- FIGURE 1.1: PLATING MATERIALS FOR ADVANCED PACKAGING AND INTERCONNECT REVENUES ($M'S)

- FIGURE 1.2. WAFERS/YR & % OF PACKAGING THAT IS ADVANCED PACKAGING (AP)

- FIGURE 1.3: ADV LOGIC DEVICE GROWTH FORECAST

- FIGURE 1.4: COPPER PLATING CHEMICALS REVENUES ($M'S) FOR ADVANCED PACKAGING & FE CU INTERCONNECTS

- FIGURE 1.5: 2023 SUPPLIER MARKET SHARES CU PLATING FOR INTERCONNECT ADDITIVES

- FIGURE 1.6: 2023 SUPPLIER MARKET SHARES CU PLATING FOR ADV. PACKAGING

- FIGURE 3.1: GLOBAL ECONOMY AND THE ELECTRONICS SUPPLY CHAIN (2023)

- FIGURE 3.2: WORLDWIDE SEMICONDUCTOR SALES

- FIGURE 3.3: TECHCET'S TAIWAN SEMICONDUCTOR INDUSTRY INDEX (TTSII) IN 000'S OF NTD

- FIGURE 3.4: 2023 SEMICONDUCTOR CHIP APPLICATIONS

- FIGURE 3.5: GLOBAL LIGHT VEHICLE UNIT SALES

- FIGURE 3.6: ELECTRIFICATION TREND BY WORLD REGION

- FIGURE 3.7: AUTOMOTIVE SEMICONDUCTOR PRODUCTION

- FIGURE 3.8: MOBILE PHONE SHIPMENTS, WW ESTIMATES

- FIGURE 3.9: WORLDWIDE PC AND TABLET FORECAST

- FIGURE 3.9: WORLDWIDE PC AND TABLET FORECAST

- FIGURE 3.10: TSMC PHOENIX CAMPUS WITH THE 2ND FAB VISIBLE IN THE BACKGROUND

- FIGURE 3.11: ESTIMATED GLOBAL FAB SPENDING 2023-2028

- FIGURE 3.12: FAB EXPANSIONS WITHIN THE US

- FIGURE 3.13: SEMICONDUCTOR CHIP MANUFACTURING REGIONS OF THE WORLD

- FIGURE 3.14: GLOBAL TOTAL EQUIPMENT SPENDING (US$ M) AND Y-O-Y CHANGE

- FIGURE 3.15: ADVANCED LOGIC DEVICE TECHNOLOGY ROADMAP OVERVIEW

- FIGURE 3.16: DRAM TECHNOLOGY ROADMAP OVERVIEW

- FIGURE 3.17: 3D NAND TECHNOLOGY ROADMAP OVERVIEW

- FIGURE 3.18: INTEL OHIO PLANT SITE AS OF FEB. 2024

- FIGURE 3.19: TECHCET WAFER START FORECAST BY NODE SEGMENTS

- FIGURE 3.20: TECHCET WORLDWIDE MATERIALS FORECAST ($M USD)

- FIGURE 4.1: PACKAGING METALLIZATION APPLICATIONS

- FIGURE 4.2: USE OF SILICON INTERPOSER IN 2.5D PACKAGING

- FIGURE 4.3: VERSIONS OF TSV & PROCESS FLOW EXAMPLE

- FIGURE 4.4: PLATING MATERIALS FOR ADVANCED PACKAGING AND DEVICE INTERCONNECT REVENUES (M'S)

- FIGURE 4.5: CU PLATING CHEMICALS 5-YEAR FORECAST

- FIGURE 4.6: WAFERS/YR & % OF PACKAGING THAT IS ADVANCED PACKAGING

- FIGURE 4.7: REVENUE FORECAST CU PLATING ADVANCED PACKAGING

- FIGURE 4.8: CU PILLAR & CU RDL SEGMENTED FORECAST

- FIGURE 4.9: ADV. PACKAGING CU CUSO4 AMOUNT DEMAND FORECAST

- FIGURE 4.10: ADV. PACKAGING CU/VMS VOLUME DEMAND FORECAST ADV.PACKAGING CU PLATING ADDITIVES

- FIGURE 4.11: BUMPING MATERIALS FOR FIRST LEVEL INTERCONNECT

- FIGURE 4.12: HYBRID BONDING PROCESS

- FIGURE 4.13: SN AND SNAG PLATING REVENUE

- FIGURE 4.14: NICKEL PLATING REVENUE

- FIGURE 4.15: ADV LOGIC DEVICE GROWTH FORECAST

- FIGURE 4.16: METAL PLATING WAFER PASSES

- FIGURE 4.17: WW DAMASCENE REVENUE FORECAST ESTIMATES

- FIGURE 4.18: DAMASCENE CUSO4 VOLUME DEMAND FORECAST

- FIGURE 4.19: DAMASCENE CU PLATING CHEMICAL AMOUNT DEMAND FORECAST

- FIGURE 5.1: KEY TRENDS IN ADVANCED PACKAGING

- FIGURE 5.2: CHALLENGES OF ELECTROPLATING VIA FILL

- FIGURE 5.3: METAL INTERCONNECTS BY LOGIC NODE

- FIGURE 5.4: INTERCONNECT METAL COMPARISON BY RESISTIVITY

- FIGURE 5.5: CU CHIP INTERCONNECTS QUALIFICATION

- FIGURE 5.6: LEADING EDGE LOGIC POWER RAIL SCHEMES

- FIGURE 5.7: DRAM STRUCTURE

- FIGURE 5.8: 3D NAND STRUCTURE

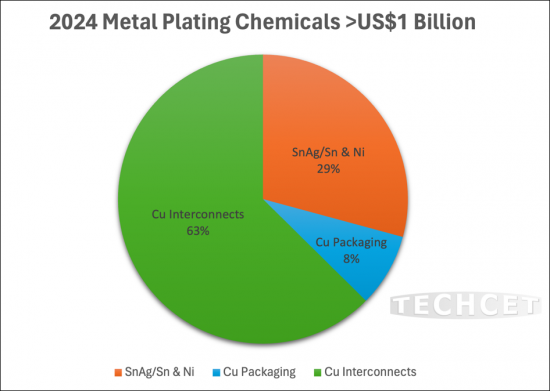

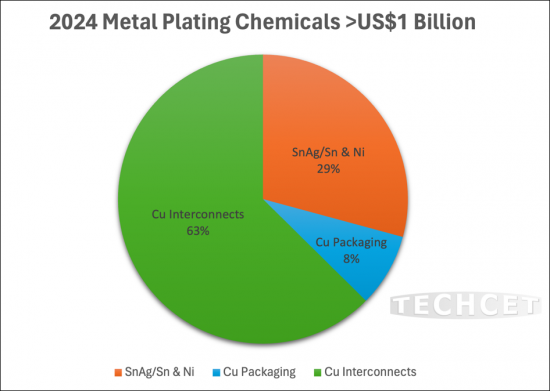

- FIGURE 6.1: TOTAL PLATING FOR ADV. PACKAGING AND CU INTERCONNECT ADDITIVES 2023

- FIGURE 6.2: PLATING EQUIPMENT OEM MARKET SHARES % 2023

- FIGURE 6.3: PLATING CHEMICAL SUPPLIER FOR INTERCONNECTS AND ADVANCED PACKAGING APPLICATIONS

- FIGURE 9.1: CLEANING COMPLEXITY

- FIGURE 9.2: OSATS PACKAGING BUSINESS CANNIBALIZATION TREND

- FIGURE 9.3: WAFER LEVEL PLATING

- FIGURE 9.4: ADVANCED PACKAGING MARKET DRIVERS AND APPLICATIONS

- FIGURE 9.4: ADVANCED PACKAGING MARKET DRIVERS AND APPLICATIONS

- FIGURE 9.5: FAN-IN (WLCSP) & FAN-OUT (WLFO) COMPARISON

- FIGURE 9.6: RDL CIRCUITRY EXAMPLE

- FIGURE 9.7: COMPARISON WITH DAMASCENE- TYPE RDL

- FIGURE 9.8: COST/PERFORMANCE IMPROVEMENTS THROUGH CHIPLETS INTEGRATION

- FIGURE 9.9: 2.5 AND 3D PACKAGING EXAMPLES

- FIGURE 9.10: USE OF SILICON INTERPOSER

- FIGURE 9.11: TSV PROCESS FLOW EXAMPLE

- FIGURE 9.12: PROCESS COMPARISON OF TRADITIONAL VS. WLP FLOWS

LIST OF TABLES

- TABLE 3.2: BATTERY ELECTRIC VEHICLE (BEV) REGIONAL TRENDS

- TABLE 3.3: DATA CENTER SYSTEMS AND COMMUNICATION SERVICES MARKET SPENDING 2023

- TABLE 5.1: IRDS 2023 MORE MOORE INTERCONNECT ROADMAP

- TABLE 5.2: BARRIER METAL ROADMAP

- TABLE 5.3: METALS REQUIRED FOR DEVICE FEATURES

- TABLE 5.4: DRAM USE OF MO OR RU PRESENT & FUTURE

- TABLE 5.5: GENERAL PROCESS FLOW ADVANCED DRAM

- TABLE 5.5: 3D NAND MATERIAL CHANGES PRESENT & FUTURE

- TABLE 5.6: NUMBER OF STACKS (S) & LAYERS (L) PER GENERATION OF 3DNAND - SOME ARE ESTIMATES FOR THE FUTURE

- TABLE 5.7: EXAMPLE OF LOGIC PROCESS FLOW 20 NM TO 32 NM LOGIC PVD

- TABLE 5.8: TECHNICAL REQUIREMENTS SUMMARY

- TABLE 5.9: TECHNICAL REQUIREMENTS SUMMARY, CONTINUED

- TABLE 6.1: REGIONAL PLAYERS - MARKET LEADER AND "OTHERS"

- TABLE 9.1: CU PACKAGING APPLICATIONS AND REQUIREMENTS

02-2729-4219

+886-2-2729-4219